| Title           | Dr.            | First Name    | Manoj                           | Last Name  | Saxena | Photograph            |

|-----------------|----------------|---------------|---------------------------------|------------|--------|-----------------------|

| Designation     | ·              | Assistant Pro | fessor                          |            |        |                       |

| Address         |                | Department of | Department of Electronics       |            |        |                       |

|                 |                | Deen Dayal U  | padhyaya Col                    | lege       |        |                       |

|                 |                | University of | Delhi                           |            |        |                       |

|                 |                | Karampura, N  | lew Delhi-110                   | 015, India |        |                       |

| Phone No C      | Office         | 011-2545817   | 3                               |            |        |                       |

| R               | esidence       | 011-2853141   | 011-28531418                    |            |        |                       |

| Mobile<br>Email |                | 09968393104   | 09968393104<br>msaxena@ieee.org |            |        |                       |

|                 |                | msaxena@ie    |                                 |            |        |                       |

| Web-Page        |                | http://people | e.du.ac.in/~m                   | saxena/    |        |                       |

| Educational C   | Qualifications |               |                                 |            |        |                       |

| Degree          |                | Institution   |                                 |            |        | Year                  |

| Ph.D. Electro   | nics           | University of | Delhi                           |            |        | 2006                  |

| M. Sc. Electro  | onics          | University of | Delhi                           |            |        | 2000 (Gold Medallist) |

| B. Sc. (H) Elec | ctronics       | University of | Delhi                           |            |        | 1998                  |

| Career Profile  | 2              |               |                                 |            |        |                       |

- Lecturer, Department of Electronics, Deen Dayal Upadhyaya College, University of Delhi (August 2000 December 2005)

- Assistant Professor, Department of Electronics, Deen Dayal Upadhyaya College, University of Delhi (01/01/2006 30/08/2006)

- Assistant Professor (Lecturer in Senior Scale), Department of Electronics, Deen Dayal Upadhyaya College, University of Delhi (30/08/2006 Till Date)

# Administrative Assignments

#### Year 2011 - 2012

- Convener-Career Counseling and Placement Cell

- Member-Admission Committee

- Member Alumni Committee of College

- Member Departmental Technical and Purchase Committee

## Year 2010 - 2011

- Convener Placement Cell

- Member Gandhi Study Circle, DDU College

- Member Rajiv Gandhi Study Circle, DDU College

- Member Alumni Committee of College

- Member Departmental Technical and Purchase Committee

- Member Lab. Development Committee for Labs in New Block

#### Year 2009 - 2010

- Convener Aryabhatta Science Forum

- Member Gandhi Study Circle, DDU College

- Member Rajiv Gandhi Study Circle, DDU College

- Member Prospectus Committee

- Member Canteen Committee

- Member Committee for purchase of office automation software for college

- Member Committee for renovation of furniture for staff room, principal office and seminar room of college

#### Year 2008 - 2009

- Convener Prospectus Committee

- Member Magazine Committee

- Member Canteen Committee

- Member Placement Cell

- Member Admission Committee

- Member Website Committee

- Member Aryabhatta Science Forum

#### Year 2007 - 2008

- Convener College Prospectus Committee

- Co-Convener Time Table Committee

- Treasurer- DDUC Teaching Staff Association

- Member College Placement Cell

- Member Admission Committee

- Member Library Stock Verification Committee

#### Year 2006 - 2007

- Convener College Prospectus Committee

- Member College Placement Cell

- Member Admission Committee

- Member Library Stock Verification Committee

- Member Purchase Committee

- Member Departmental Lab. maintenance Committee

## Year 2005 - 2006

- Member Student Activity Committee

- Member College Prospectus Committee

- Member College Website Committee

- Member Departmental Purchase Committee

- Member College Infrastructure Development Committee

- Member Proctorial Board

- Member Aryabhatta Science Forum

- Member Library Stock Verification Committee

- Member Admission Committee

- Member Purchase Committee

- Treasurer- DDUC Teaching Staff Association

#### Year 2004 - 2005

- Member Technical Library Purchase Committee.

- Member Library Stock Verification Committee

- Member Departmental Technical Committee

- Member Departmental Time Table Committee

- Member Student Activity Committee

- Member Prospectus Committee

- Member Website Development Committee

## Year 2003 - 2004

- Member Technical purchase Committee

- Member Discipline Committee

- Member Sports Committee

# Areas of Interest / Specialization

Modeling and simulation of sub-100 nm MOSFET structures:

- Epitaxial Channel and Drain Engineered

- Dual/ Tripple Material Gate (DMG/ TMG)

- Silicon on Nothing (SON)

- Insulated Shallow Extension (ISE)

- Recessed Channel/ Grooved/ Concave Gate

- Tunnel FET

- Optically Controlled FET (OPFET)

- Mercuric Iodide (HgI<sub>2</sub>) X-Ray Detectors

# Subjects Taught

# Post Graduate Level (As Visiting Faculty)

| Course                                                                                                                                                          | Year                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M. Sc Electronics (IV <sup>th</sup> Semester) - VLSI Circuit Design and Device Modelling – 4.2 (Deptt. Of Electronic Science, University of Delhi South Campus) | January 2011 – April 2011                                                                                                                                                  |

| M. Sc Electronics (I <sup>st</sup> Semester) - Advance Analog and Digital Electronics - 1.4 (Deptt. Of Electronic Science, University of Delhi South Campus)    | July 2011 – December 2011<br>July 2010 – December 2010<br>July 2009 – December 2009<br>July 2008 – December 2008<br>July 2005 – December 2005<br>July 2004 – December 2004 |

| M. Sc Informatics – Introduction to Communication Systems – IT-13 (Institute of Informatics & Communication, University of Delhi South Campus)                  | 2005-2006                                                                                                                                                                  |

## **Under Graduate Level**

| Course                                                                        | Year                                                                       |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| B. Sc. (H) Electronics I Semester – Network Analysis                          | 2010-2011                                                                  |

| B. Sc. (H) Electronics II Semester – Signal and Systems                       | 2010-2011                                                                  |

| B. Sc. (H) Electronics I year – Network Analysis and Linear Active circuits   | 2009-2010<br>2008-2009<br>2007-2008<br>2004-2005<br>2003-2004<br>2002-2003 |

| B. Sc. (H) Electronics II year – Operational Amplifier and Analog Computation | 2009-2010<br>2008-2009<br>2007-2008<br>2006-2007<br>2005-2006              |

| B. Sc. (H) Electronics II year – Numerical analysis and FORTRAN programming   | 2008-2009<br>2007-2008                                                     |

| B. Sc. (H) Ele                                                                                                               | ectronics III year – E                                                                                               | ngineering Drawing                                                  |                                                                                           |                                         | 200            | 3-2004               |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------|----------------|----------------------|

| B. Sc. (H) Electronics III year – Power Electronics                                                                          |                                                                                                                      |                                                                     |                                                                                           | 6-2007<br>5-2006                        |                |                      |

| B. Sc. (H) Electronics III year – Communication System                                                                       |                                                                                                                      |                                                                     | 200                                                                                       | 3-2004                                  |                |                      |

| B. Sc (H) Computer Science I semester - Digital Electronics                                                                  |                                                                                                                      |                                                                     | 200<br>200                                                                                | 2-2003<br>16-2007<br>15-2006<br>14-2005 |                |                      |

| B. Sc (H) Co                                                                                                                 | mputer Science II se                                                                                                 | mester - Analog Ele                                                 | ctronics                                                                                  |                                         | 200            | 3-2004               |

| B. Sc (H) Co                                                                                                                 | mputer Science V se                                                                                                  | mester - Microproc                                                  | essor                                                                                     |                                         |                | 4-2005<br>3-2004     |

| Research Gui                                                                                                                 | idance                                                                                                               |                                                                     |                                                                                           |                                         |                |                      |

| Supervision<br>Supervision<br>Supervision<br>Supervision                                                                     | each head (If applica<br>of awarded Doctora<br>of Doctoral Thesis, u<br>of awarded M.Phil o<br>of M.Phil dissertatio | Il Thesis<br>Inder progress<br>Iissertations<br>Ins, under progress | Nil<br>One<br>Three<br>Nil                                                                |                                         |                |                      |

| oint Supervi                                                                                                                 |                                                                                                                      |                                                                     |                                                                                           |                                         |                |                      |

| S. No.                                                                                                                       | Tit                                                                                                                  |                                                                     |                                                                                           | ame and Affiliation                     | Year           | Status               |

| 1.                                                                                                                           | Modeling and Nanoscale Dual Insulated Shallow E Nothing MOSFET for power applications                                | Material Gate xtension Silicon on                                   | Ms. Vandana Kumari, I<br>UGC-NET (LS)<br>Department of Electro<br>University of Delhi Sou |                                         | Jan<br>2010    | On Going             |

| Supervision (                                                                                                                | of M. Phil dissertation                                                                                              | on                                                                  |                                                                                           |                                         |                |                      |

|                                                                                                                              | of the                                                                                                               | Title of the Dissert                                                | ation                                                                                     | University/ Roll.<br>No.                | Year/<br>Statu |                      |

| Ms. Rakhi N                                                                                                                  | Narang                                                                                                               |                                                                     | ain-Leakage Current<br>pleted Double-Gate                                                 | Reg. No – 605011080014                  | 2009,          | <sup>7</sup> Awarded |

| Ms. Sonia A                                                                                                                  | hlawat                                                                                                               |                                                                     | lysis of Body Potential<br>-All-Around Nanowire                                           | Reg. No -605011080015                   | 2009,          | <sup>/</sup> Awarded |

| Ms. Neha Microwave Modeling and Parameter Reg. No – 2009/ Awarded extraction method for Quantum Well C8HR016M1250029 Laser   |                                                                                                                      | <sup>/</sup> Awarded                                                |                                                                                           |                                         |                |                      |

|                                                                                                                              | he Research Scholar                                                                                                  |                                                                     | 0 111.1                                                                                   | L A CCUL                                |                | CL :                 |

| S. No.                                                                                                                       | Tit                                                                                                                  |                                                                     |                                                                                           | ame and Affiliation                     | Year           | Status               |

| <ol> <li>Analytical Modeling and Simulation of Tunnel FET</li> <li>UGC-JRF-NET, Department of Electronic Science,</li> </ol> |                                                                                                                      | Jan<br>2010                                                         | On Going                                                                                  |                                         |                |                      |

|                                                                                                                              |                                                                                                                      |                                                                     |                                                                                           | th Campus, New Delhi.                   |                |                      |

| 2. | Analytical Modeling and Simulation of | Ms. Rajni Gautam, Research Scholar,          | Jan  | On Going |

|----|---------------------------------------|----------------------------------------------|------|----------|

|    | Optically Controlled FET (OPFET)      | UGC-JRF-NET,                                 | 2010 |          |

|    |                                       | Department of Electronic Science,            |      |          |

|    |                                       | University of Delhi South Campus, New Delhi. |      |          |

# **Project Guidance/ Supervision**

# **At National Level**

(Summer Research Fellowship Sponsored by Indian Academy of Sciences (IAS), National Academy of Sciences, India (NASI) & Indian National Science Academy (INSA))

| S. No. | Title                                                                                                                            | Candidate's name and Affiliation                                                                                                            | Duration     | Status    |

|--------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|

| 1.     | Computer Aided Analysis,<br>Charecterization, Optimization and<br>Simulation of Bio-Molecules of Field<br>Effect Biosensors      | Jagriti Mishra B. Tech, BITS Meshra (ENGS1368)                                                                                              | May-July2010 | Completed |

| 2.     | Analytical modeling and Simulation of<br>Short Channel Effects and Quantum-<br>Confinement Effects in Silicon Nanowire<br>MOSFET | Gaurav Mahajan<br>B.E. (Hons.) Electrical and Electronics<br>Engineering<br>Birla Institute of Technology and Science,<br>Pilani (ENGS2982) | May-July2010 | Completed |

| 3.     | Analytical modeling and Simulation of<br>Germanium on Insulator MOSFET for<br>Optical Application                                | Neha Bhushan<br>KIIT University, Bhubaneswar<br>(ENGS2269)                                                                                  | May-July2011 | Completed |

| 4.     | Analytical modeling and simulation of Tunnel FET for Sensor application                                                          | K V Sasidhar Reddy<br>NIT, Warangal<br>(ENGS4147)                                                                                           | May-July2011 | Completed |

# **Publications Profile**

**Total Publications: 130**

International Refereed Journals 37

International Conferences 66

National Conferences 24

Year wise summary of papers published in Journals and Conferences

| Year  | International Journal | International<br>Conferences | National Conferences | Total |

|-------|-----------------------|------------------------------|----------------------|-------|

| 2002  | 01                    |                              |                      | 01    |

| 2003  | 02                    | 01                           |                      | 03    |

| 2004  | 03                    | 04                           | 01                   | 08    |

| 2005  | 03                    | 06                           | 02                   | 11    |

| 2006  | 02                    | 03                           | 05                   | 10    |

| 2007  | 06                    | 13                           | 03                   | 22    |

| 2008  | 08                    | 17                           | 03                   | 28    |

| 2009  | 04                    | 02                           |                      | 06    |

| 2010  | 02                    | 02                           |                      | 04    |

| 2011  | 06                    | 21                           | 10                   | 37    |

| Total | 37                    | 69                           | 24                   | 130   |

#### International Journals where papers have been published (ISI Thomson Impact Factor: 2010)

| Publication title                                                                           | Impact factor | No. of Papers |

|---------------------------------------------------------------------------------------------|---------------|---------------|

| IEEE Trans on Electron Devices, USA                                                         | 2.730         | 09            |

| Semiconductor Science Technology, Institute of Physics (IOP), UK                            | 1.434         | 06            |

| Microelectronic Engineering, Elsevier, UK                                                   | 1.583         | 02            |

| Superlattices and Microstructures, Elsevier, UK                                             | 1.211         | 02            |

| Solid-state Electronics, Elsevier, UK                                                       | 1.422         | 03            |

| IEE Electronics Letters, UK                                                                 | 1.140         | 01            |

| Microwave and Optical Technology Letter                                                     | 0.743         | 02            |

| International Journal of Numerical Modeling: Electronic Networks, Devices and Fields, Wiley | 0.509         | 01            |

| Journal of Semiconductor Science and Technology (JSTS)                                      |               | 02            |

| International Journal of High Speed Electronics and Systems (IJHSES)                        |               | 01            |

| International Journal of Microwave and Optical Technology Letter (IJMOT)                    |               | 02            |

#### **Invited Talk Delivered:**

- 1. "Applications of Quantum Mechanics in Nanoscale Electronics", Second National Workshop On Quantum Mechanics: Theory and Application Organized By FiDAS, Deen Dayal Upadhyaya College, University of Delhi, Sponsored By CSIR, Govt of India Supported By IEEE EDS Delhi Chapter, New Delhi and The National Academy of Sciences, India, Delhi Chapter held during October 22-23, 2010 and October 29-30, 2010.

- 2. **"Applications of Quantum Mechanics in Nanoscale Electronics: Size Quantization Effect"**, Physics Workshop organized by Kendriya Vidyalaya, R. K. Puram, Sector-2, New Delhi from December 24, 2010 to January 02, 2011

- 3. "Quantum Mechanics for Nanoelectronics" in Continuing Education Program (CEP) on "Nanoelectronics" from 17th 21st January 2011 organized by Solid State Physics Laboratory, (laboratory under the Defence Research & Development Organization (DRDO), Govt. of India)

# Books/Monographs (Authored/Edited)

• Book Chapter - MOSFET Modeling, R. S. Gupta, Mridula Gupta and Manoj Saxena, Encyclopedia of RF and Microwave Engineering, John-Wiley & Sons, Inc. New Jersey, USA, March 2005, pp. 3278-3317, ISBN: 0-471-27053-9.

## Research papers published in Refereed/Peer Reviewed Journals

#### 2002

1. Physics Based Analytical Modeling of Potential and Electrical Field Distribution in Dual Material Gate (DMG)-MOSFET for Improved Hot Electron Effect and Carrier Transport Efficiency, **Manoj Saxena**, Subhasis Haldar, Mridula Gupta, and R. S. Gupta, IEEE Transaction on Electron Devices, Vol. 49, No. 11, pp. 1928-1938, November 2002

#### 2003

- 2. Physics Based Modeling and Simulation of Dual Material Gate Stack (DUMGAS) MOSFET, **Manoj Saxena**, Subhasis Haldar, Mridula Gupta and R. S. Gupta, IEE Electronics Letter, 9th January, Vol. 39, No.1, pp-155-157, January 2003.

- 3. Modeling and simulation of asymmetric gate stack (ASYMGAS)-MOSFET, **Manoj Saxena**, Subhasis Haldar, Mridula Gupta and R. S. Gupta, Solid State Electronics, Vol. 47, pp. 2131-2134, 2003.

## 2004

- 4. Design considerations for novel device architecture: Hetro -Material Double-Gate (HEM-DG) MOSFET with sub -100 nm gate length **Manoj Saxena**, Subhasis Haldar, Mridula Gupta and R.S. Gupta, Solid State Electronics Vol. 48, pp. 1169-1174, 2004.

- 5. Optimization of Gate stack MOSFETs with Quantization effects, Tina Mangla, Amit Sehgal, **Manoj Saxena**, Subhasis Haldar, Mridula Gupta and R. S. Gupta, Journal of Semiconductor Science and Technology (JSTS), Vol.4, No.3, pp. 228-239, September 2004.

- 6. Two-Dimensional Analytical Modeling and Simulation of Retrograde doped HMG MOSFET, Kirti Goel, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, International Journal of High Speed Electronics and Systems, Vol.14, No.3, pp.676-683, September 2004.

2005

- 7. Two-Dimensional Analytical Threshold Voltage Model for Dual Material Gate (DMG) Epi-MOSFET, Kirti Goel, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, IEEE Transactions on Electron Devices, Vol.52, No.1, pp.23-29, January 2005.

- 8. Physics-based algorithm implementation for characterization of gate dielectric engineered MOSFETs including Quantization effects, Tina Mangla, Amit Sehgal, **Manoj Saxena**, Subhasis Haldar, Mridula Gupta and R. S. Gupta, Journal of Semiconductor Science and Technology (JSTS), Vol.5, No.3, pp.69-77, September 2005.

- 9. Modeling and Simulation of Stacked Gate Oxide (STGO) Architecture in Silicon-On-Nothing (SON) MOSFET Poonam Kasturi, **Manoj Saxena** and R.S. Gupta, Solid State Electronics, Vol. 49, No. 10, pp. 1639-1648,October 2005.

#### 2006

- 10. Modeling and Simulation of a Nanoscale Three Region Tri MAterial Gate Stack (TRIMGAS) MOSFET for Improved Carrier Transport Efficiency and Reduced Hot Electron Effects, IEEE Transactions on Electron Devices, Kirti Goel, **Manoj Saxena**, Mridula Gupta and R. S. Gupta, Vol. 53, No. 7, pp. 1623-1633, July 2006.

- 11. Two-Dimensional Analysis and Simulation for Gate Stack Silicon-On-Nothing MOSFET (GAS-SON MOSFET), Poonam Kasturi, Manoj Saxena, R.S. Gupta, International Journal of Microwave and Optical Technology Letter (IJMOT), Vol. 1, No. 2, pp. 417-421, August 2006.

#### 2007

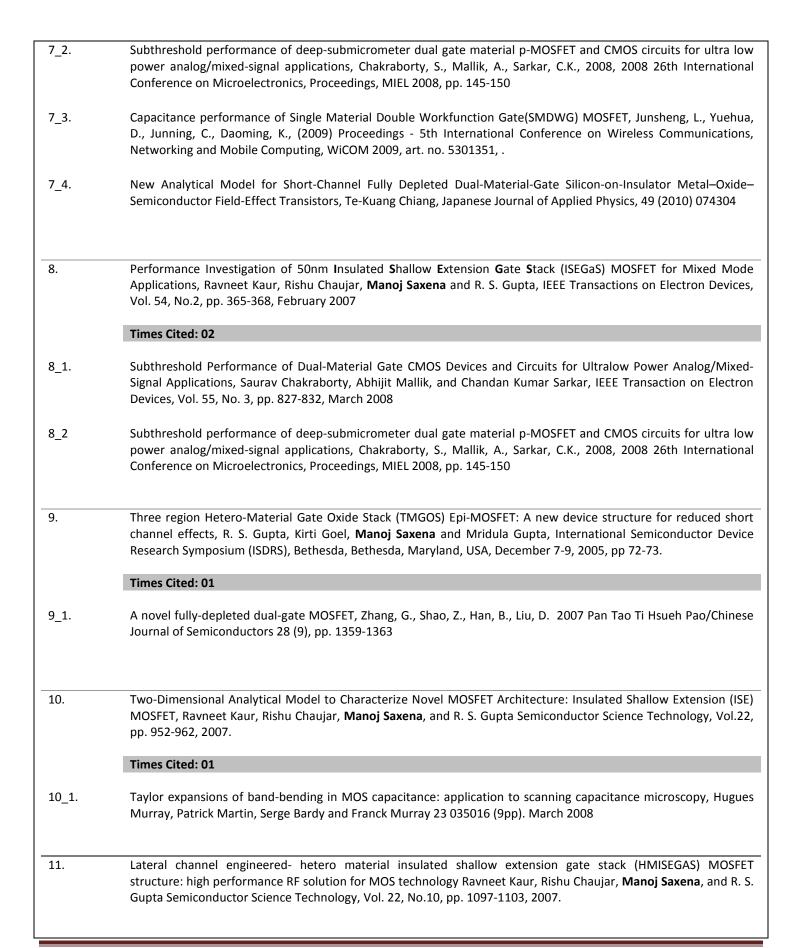

- 12. Performance Investigation of 50nm Insulated Shallow Extension Gate Stack (ISEGaS) MOSFET for Mixed Mode Applications, Ravneet Kaur, Rishu Chaujar, **Manoj Saxena** and R. S. Gupta, IEEE Transactions on Electron Devices, Vol. 54, No.2, pp. 365-368, February 2007.

- 13. Unified model for physics based modeling of a new device architecture: Triple Material Gate Oxide Stack Epitaxial Channel Profile (TRIMGASEpi) MOSFET, Kirti Goel, **Manoj Saxena**, Mridula Gupta and R. S. Gupta, Semiconductor Science and Technology, vol. 22, pp. 435-446, 2007.

- 14. Hot carrier reliability and analog performance investigation of DMG-ISEGaS MOSFET Ravneet Kaur, Rishu Chaujar, **Manoj Saxena**, and R. S. Gupta, IEEE Transactions on Electron Devices, Vol. 54, No. 9, pp. 2556-2561, September 2007.

- 15. Unified Subthreshold Model for Channel Engineered Sub-100nm Advanced MOSFET Structures Ravneet Kaur, Rishu Chaujar, **Manoj Saxena** and R. S. Gupta, IEEE Transactions on Electron Devices Vol. 54, No. 9, pp. 2475-2486, September 2007.

- 16. Two-Dimensional Analytical Model to Characterize Novel MOSFET Architecture: Insulated Shallow Extension (ISE) MOSFET, Ravneet Kaur, Rishu Chaujar, **Manoj Saxena**, and R. S. Gupta Semiconductor Science Technology, Vol.22, pp. 952-962, 2007.

- 17. Lateral channel engineered- hetero material insulated shallow extension gate stack (HMISEGAS) MOSFET structure: high performance RF solution for MOS technology Ravneet Kaur, Rishu Chaujar, **Manoj Saxena**, and R. S. Gupta Semiconductor Science Technology, Vol. 22, No.10, pp. 1097-1103, 2007.

#### 2008

- 18. Dual Material Double Layer Gate Stack SON MOSFET: A Novel Architecture for enhanced analog performance Part I Impact of Gate Metal Workfunction Engineering, Poonam Kasturi, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, IEEE Transactions on Electron Devices, Vol. 55, No. 1, pp. 372-381, January 2008.

- 19. Dual Material Double Layer Gate Stack SON MOSFET: A Novel Architecture for enhanced analog performance Part II Impact of Gate Dielectric Material Engineering, Poonam Kasturi, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, IEEE Transactions on Electron Devices, Vol. 55, No. 1, pp. 382-387, January 2008.

- 20. Laterally amalgamated DUal Material GAte Concave (L-DUMGAC) MOSFET For ULSI, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R. S. Gupta, Microelectronic Engineering, Vol. 85, No. 3, pp. 566-576, March 2008.

- 21. Two-dimensional analytical sub-threshold model of multi-layered gate dielectric recessed channel (MLaG-RC) nanoscale MOSFET, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R. S. Gupta, Semiconductor Science Technology Vol.23, 045006 (10pp) 2008.

- 22. Intermodulation Distortion and Linearity Performance Assessment of 50-nm gate length L-DUMGAC MOSFET for RFIC Design, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, Superlattices and Microstructures, Vol.44, pp. 143-152, 2008.

- 23. On-state and RF performance investigation of sub-50nm L-DUMGAC MOSFET design for high-speed logic and switching applications, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R. S. Gupta, Semiconductor Science Technology, **23** 095009 (8pp), 2008.

- 24. TCAD Assessment of Gate Electrode Workfunction Engineered Recessed Channel (GEWE-RC) MOSFET and its Multi-Layered Gate Architecture: Part-I: Hot Carrier Reliability Evaluation, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, IEEE Transactions on Electron Devices, Vol. 55, No. 10, pp. 2602-2613, October 2008.

25. A TCAD Study of Sub-100nm Advance Gate Electrode Workfunction Engineered SON MOSFET, R S Gupta, **Manoj Saxena** and Poonam Kasturi, International Journal of Microwave and Optical Technology Letter (IJMOT), Vol. 3, No. 3, pp. 190-195, July 2008.

#### 2009

- 26. Investigation of Multi-Layered-Gate Electrode Workfunction Engineered Recessed Channel (MLGEWE-RC) Sub-50nm MOSFET: A Novel Design, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, International Journal of Numerical Modeling: Electronic Networks, Devices and Fields, Wiley, Vol. 22, No. 3, pp. 259-278, March/ April 2009.

- 27. Two-dimensional threshold voltage model and design considerations for gate electrode workfunction engineered recessed channel (GEWE-RC) nanoscale MOSFET: part I, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, Semiconductor Science Technology, Vol. **24**, No 6, 065005 (10pp), (June 2009)

- 28. Two Dimensional Simulation and Analytical Modeling of a Novel ISE MOSFET with Gate Stack Configuration, Ravneet Kaur, Rishu Chaujar, **Manoj Saxena**, Mridula Gupta and R. S. Gupta, Microelectronic Engineering, Volume 86, Issue 10, Pages 2005-2014, October 2009

- 29. TCAD assessment of Gate Electrode Workfunction Engineered Recessed Channel (GEWE-RC) MOSFET and its multi-layered gate architecture, Part II: Analog and large signal performance evaluation, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, Superlattices and Microstructures, Volume 46, Issue 4, Pages 645-655, October 2009

#### 2010

- 30. Hot-Carrier Reliability Monitoring of DMG ISE SON MOSFET for improved Performance, Ravneet Kaur, Rishu Chaujar, **Manoj Saxena** and R.S. Gupta, Microwave and Optical Technology Letter, pp. 652-657, Vol. 52, No. 3, March 2010.

- 31. Design Considerations and Impact of Technological papramteric variations on RF/Microwave performance of GEWE-RC MOSFET, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, Microwave and Optical Technology Letter, pp. 770-775, Vol. 52, No. 3, March 2010.

#### 2011

- 32. Channel Material Engineered Nanoscale Cylindrical Surrounding Gate MOSFET with Interface Fixed Charges, Rajni Gautam, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, TRENDS IN NETWORK AND COMMUNICATIONS Communications in Computer and Information Science, Volume 197, Part 2, 476-485, 2011

- 33. Effect of Temperature and Gate Stack on the Linearity and Analog Performance of Double Gate Tunnel FET, Rakhi Narang, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, TRENDS IN NETWORK AND COMMUNICATIONS Communications in Computer and Information Science, 2011, Volume 197, Part 2, 466-475, 2011

- 34. Impact of Interface Fixed Charges on the Performance of the Channel Material Engineered Cylindrical Nanowire MOSFET, Rajni Gautam, **Manoj Saxena**, R. S. Gupta, and Mridula Gupta, *International journal of VLSI design & Communication Systems (VLSICS ), Vol. 2, No. 3, pp. 225-241, September 2011*

- 35. Linearity and Analog Performance analysis of Double Gate Tunnel FET: Effect Temperature and Gate Stack, Rakhi Narang, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, *International journal of VLSI design & Communication Systems (VLSICS)*, Vol. 2, No. 3, pp. 185-200, September 2011

- 36. Two Dimensional Analytical Subthreshold Model of Nanoscale Cylindrical Surrounding Gate MOSFET Including Impact of Localised Charges, Rajni Gautam, Manoj Saxena, Mridula Gupta and R. S. Gupta, Accepted for Publication in Journal of Computational and Theoretical Nanoscience (CTN).

- 37. Fabrication and Time Degradation study of Mercuric Iodide (Red) Single Crystal X-Ray Detector, Kulvinder Singh, **Manoj Saxena**, J. Nano- Electron. Phys.3 (2011) No. 1, pp. 802-807, 2011

# Research papers published in Refereed/Peer Reviewed Conferences

# Paper Published in International conferences: -

#### 2003

Closed form Analytical Threshold Voltage Model of Dual Material Double-Gate (DUM-DG) MOSFET, Manoj Saxena, Subhasis Haldar, Mridula Gupta, and R. S. Gupta, 15<sup>th</sup> Asia Pacific Microwave Conference (APMC-2003), November 4-7, 2003, Seoul, Korea, pp. 1434-1437.

#### 2004

- 2. Two-Dimensional analytical modeling and simulation of retrograde doped HMG-MOSFET, R. S. Gupta, Kirti Goel, **Manoj Saxena** and Mridula Gupta, **IEEE Lester Eastman Conference**, August 4-6, 2004, Troy, New York, USA, pp. 84-85.

- 3. Physics Based Modeling and Simulation of Epitaxial Channel Hetero Material Gate Stack (EPI-HEMGAS MOSFET), Kirti Goel, Manoj Saxena, Mridula Gupta and R. S. Gupta, 16<sup>th</sup> Asia Pacific microwave Conference, APMC, December 15<sup>th</sup> –18<sup>th</sup>, 2004, New Delhi, India, pp. 9-10.

- 4. Analytical Analysis and Simulation of High-K Dielectric in Gate Stack Silicon on Nothing (GAS-SON) MOSFET for Sub-100 nm Gate Length, Poonam Kasturi, **Manoj Saxena**, R.S. Gupta, **16**<sup>th</sup> **Asia Pacific Microwave Conference, APMC**, December 15<sup>th</sup> –18<sup>th</sup>, 2004, New Delhi, India, pp. 65-67

- 5. HEMGAS: A Novel Gate Workfunction Engineered Stacked Gate Oxide Concept for Sub-50 nm DG-MOSFET, **Manoj Saxena**, Subhasis Haldar, Mridula Gupta, and R. S. Gupta, 2<sup>nd</sup> **International conference on Computer and Devices for communications, CODEC-2004**, January 1-3, 2004 in Calcutta, India, pp. 155

## 2005

- Two-Dimensional Analysis and Simulation for Gate Stack Silicon-On-Nothing MOSFET (GAS-SON MOSFET), Poonam Kasturi, Manoj Saxena, R.S. Gupta, 10<sup>th</sup> International Symposium on Microwave and Optical Technology, ISMOT 2005, Fukuoka, Japan, August 22–25, 2005, pp. 406-409

- 7. Dual-Material Gate Asymmetric Oxide (DMGASYMOX) Stack MOSFET: A Novel Device Architecture for Improved Carrier Transport Efficiency and Reduced Hot Electron Effects, Kirti Goel, **Manoj Saxena**, Mridula Gupta, R. S. Gupta **International Union of Radio Science (URSI)**, New Delhi, India, October 23-29, 2005.

- Non-Uniformly Doped Gate Electrode Workfunction Engineered MOSFET: Novel Design Architecture for Controlling Short Channel Effect and Improving Gate Transport Efficiency, R. S. Gupta, Kirti Goel, Manoj Saxena and Mridula Gupta, Thirteenth International Workshop on The Physics of Semiconductor Devices (IWPSD), New Delhi, India, December 13-17, 2005, pp. 995-1002.

- 9. Investigating the role of Stacked Gate Oxide and Hetro-Material Gate on Electrical Characteristics of Insulated Shallow Extension (ISE) MOSFET Ravneet Kaur, Manoj Saxena and R. S. Gupta, Thirteenth International Workshop on The Physics of Semiconductor Devices (IWPSD), New Delhi, India, December 13-17, 2005 pp. 1163-1166.

- 10. Physics based modeling and simulation of Hetero-Material Asymmetric Gate Stack Epi-MOSFET (HEMAGASE)-MOSFET, Kirti Goel, Manoj Saxena, Mridula Gupta, R. S. Gupta, 16th Asia Pacific Microwave Conference (APMC-2005), Suzhou, China, December 4-7, 2005, pp. 848-851.

- 11. Three Region Hetero-Material Gate Oxide Stack (TMGOS) Epi-MOSFET: A New Device Structure for Reduced Short Channel Effects, R. S. Gupta, Kirti Goel, **Manoj Saxena** and Mridula Gupta, **International Semiconductor Device Research Symposium** (ISDRS), Bethesda, Bethesda, Maryland, USA, December 7-9, 2005, pp 72-73.

#### 2006

- 12. Comparison of Three Region Multiple Gate Nanoscale Structures for Reduced Short Channel Effects and High Device Reliability, Kirti Goel, **Manoj Saxena** and Mridula Gupta and R. S. Gupta, **Workshop on Compact Modeling (WCM 06)**, Boston, Massachusetts, U.S.A., NSTI-Nanotech, pp. 816-819, May 9-11, 2006.

- 13. Gate Oxide Engineered Dual Material Gate Insulated Shallow Extension (GOXDMG-ISE) MOSFET: A New Vent to Wireless Communication, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R. S. Gupta, 3<sup>rd</sup> International Conference on Computers and Devices for Communication (CODEC-2006), Institute of Radio physics and Electronics, Calcutta, pp. 324-327, December 18-20, 2006

- 14. Exploration of the Effect of Negative Junction Depth on the Electrical Characteristics of Concave DMG MOSFET in Sub-50-Nanometer Regime, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R. S. Gupta, 3<sup>rd</sup> International Conference on Computers and Devices for Communication (CODEC-2006), Institute of Radio physics and Electronics, Calcutta, pp. 317-319, December 18-20, 2006

#### 2007

- 15. Dual Material Gate (DMG) SOI-MOSFET with Dielectric Pockets: Innovative Sub-50 nm design for improved switching performance, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R.S. Gupta, Indo-Australian Symposium on Multifunctional Nanomaterials, Nanostructures and Applications (MNNA 2007) December 19 –21, 2007, Department of Physics & Astrophysics, University of Delhi, Delhi, pp. 109

- 16. Two-Dimensional Analytical Modeling and Simulation of Rectangular Gate Recessed Channel (RG-RC) Nanoscale MOSFET in Sub-50nm Regime, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, Indo-Australian Symposium on Multifunctional Nanomaterials, Nanostructures and Applications (MNNA 2007) December 19 –21, 2007, Department of

- Physics & Astrophysics, University of Delhi, Delhi, pp. 110.

- 17. A TCAD study of sub-100 nm advance gate electrode workfunction engineered SON-MOSFET, R.S. Gupta, Manoj Saxena and Poonam Kasturi, 11<sup>th</sup> International Symposium on Microwave and Optical Technology (ISMOT-2007), Villa Mondragone, Monte Porzio Catone, Italy on 17-21 December 2007, pp. 267-270

- 18. Scrutinize the Gate Misalignment Effects in Graded Channel DG FD SOI n-MOSFET, Rupendra Kumar Sharma, Manoj Saxena, Mridula Gupta and R.S. Gupta, 11<sup>th</sup> International Symposium on Microwave and Optical Technology (ISMOT-2007), Villa Mondragone, Monte Porzio Catone, Italy on 17-21 December 2007, pp, 821-824

- 19. Electrical Characterization of Insulated Shallow Extension (ISE) MOSFET: A Punchthrough Stopper, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R.S. Gupta, 11<sup>th</sup> International Symposium on Microwave and Optical Technology (ISMOT-2007), Villa Mondragone, Monte Porzio Catone, Italy on 17-21 December 2007, pp. 813-816

- Pre-Distortion Linearity Enhancement for Sub-50nm Gate Electrode Workfunction Engineered Recessed Channel (GEWE-RC) MOSFET, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, 11<sup>th</sup> International Symposium on Microwave and Optical Technology (ISMOT-2007), Villa Mondragone, Monte Porzio Catone, Italy on 17-21 December 2007, pp.797-800

- 21. Linearity assessment in DMG ISEGaS MOSFET for RFIC Design Ravneet Kaur, Rishu Chaujar, **Manoj Saxena** and R.S. Gupta, **Nineteenth Asia Pacific Microwave Conference (APMC-2007)**, December 11-14, 2007, Bangkok, Thailand, pp.2495-2498

- 22. On-State and Switching Performance Investigation of Sub-50nm L-DUMGAC MOSFET Design for High-Speed Logic Applications, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, **International Semiconductor Device Research Symposium (ISDRS)**, University of Maryland, USA, December 12-14, 2007, pp.1892-1893

- 23. A 2-D Analytical Subthreshold Model for Gate Misalignment Effects on Graded Channel DG FD SOI n-MOSFET, Rupendra Kumar Sharma, Manoj Saxena, Mridula Gupta and R. S. Gupta, Fourteenth International Workshop on the Physics of Semiconductor Devices (IWPSD-2007) December 16-20, 2007, Mumbai, India, pp. 183-186

- 24. RF-Distortion in Sub-100nm L-DUMGAC MOSFET, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R. S. Gupta, Fourteenth International Workshop on the Physics of Semiconductor Devices (IWPSD-2007). December 16-20, 2007, Mumbai, India, pp.168-170

- 25. Two-Dimensional Analytical Threshold Voltage Model for Nanoscale SG-Concave MOSFET in Sub-50nm Regime, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, Fourteenth International Workshop on the Physics of Semiconductor Devices (IWPSD-2007), December 16-20, 2007, Mumbai, India, pp. 221-224

- 26. Nanoscale Insulated Shallow Extension MOSFET with Dual Material Gate for High Performance Analog Operations, Ravneet Kaur, Rishu Chaujar, Manoj Saxena, and R. S. Gupta, Fourteenth International Workshop on the Physics of Semiconductor Devices (IWPSD-2007) December 16-20, 2007, Mumbai, India, pp. 171-173

- 27. Performance Consideration of a Novel Architecture: ISEGaS deca-nanometer MOSFET, Ravneet Kaur, Rishu Chaujar, Manoj Saxena, and R. S. Gupta, Fourteenth International Workshop on the Physics of Semiconductor Devices (IWPSD-2007) December 16-20, 2007, Mumbai, India, pp.123-126

#### 2008

- 28. TCAD investigation of a Novel MOSFET architecure of DMG ISE SON MOSFETs for ULSI era, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R.S. Gupta, Mini-Colloquia on Compact Modeling of advance MOSFET structures and mixed mode applications on January 5-6, 2008 at University of Delhi South Campus, New Delhi, India sponsored by the IEEE Electron Device Society under its Distinguished Lecturer Program, pp. 18-19

- 29. Analytical analysis of subthreshold performance of sub-100 nm advanced MOSFET structures An iterative approach, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R.S. Gupta, Mini-Colloquia on Compact Modeling of advance MOSFET structures and mixed mode applications on January 5-6, 2008 at University of Delhi South Campus, New Delhi, India sponsored by the IEEE Electron Device Society under its Distinguished Lecturer Program, pp. 20-21

- 30. Modeling and 2-D simulation of Nanoscale SON MOSFET, Poonam Kasturi, Manoj Saxena, Mridula Gupta and R.S. Gupta, Mini-Colloquia on Compact Modeling of advance MOSFET structures and mixed mode applications on January 5-6, 2008 at University of Delhi South Campus, New Delhi, India sponsored by the IEEE Electron Device Society under its Distinguished Lecturer Program, pp. 22-24

- 31. Performance advantage of air as buried dielectric in sub-100 nm silicon-on-nothing (SON) MOSFET with gate stack architecture, Poonam Kasturi, Manoj Saxena, Mridula Gupta and R.S. Gupta, Mini-Colloquia on Compact Modeling of advance MOSFET structures and mixed mode applications on January 5-6, 2008 at University of Delhi South Campus, New Delhi, India sponsored by the IEEE Electron Device Society under its Distinguished Lecturer Program, pp. 25-26

- 32. Sub-threshold drain current performance assessment of MLGEWE-RC MOSFET for CMOS technology, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, Mini-Colloquia on Compact Modeling of advance MOSFET structures and mixed mode applications on January 5-6, 2008 at University of Delhi South Campus, New Delhi, India sponsored by the IEEE

## Electron Device Society under its Distinguished Lecturer Program, pp. 27-28

- 33. RF performance assessment of L-DUMGAC MOSFET for furure CMOS technology in gigahertz regime, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, Mini-Colloquia on Compact Modeling of advance MOSFET structures and mixed mode applications on January 5-6, 2008 at University of Delhi South Campus, New Delhi, India sponsored by the IEEE Electron Device Society under its Distinguished Lecturer Program, pp. 29-30

- 34. An Iterative Approach to Characterize Various Advanced Non-Uniformly Doped Channel Profile, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R. S. Gupta, 2008 NSTI Nanotechnology Conference and Trade Show, June 1-5, 2008, Boston, Massachusetts, U.S.A. Nanotech 2008 Vol. 3, pp. 814-817

- 35. Pre-Distortion Assessment of Workfunction Engineered Multilayer Dielectric Design of DMG ISE SON MOSFET, Ravneet Kaur, Rishu Chaujar, **Manoj Saxena** and R. S. Gupta, **2008 NSTI Nanotechnology Conference and Trade Show**, June 1-5, 2008, Boston, Massachusetts, U.S.A. Nanotech 2008 Vol. 3, pp. 605-606

- 36. Assessment of L-DUMGAC MOSFET for High Performance RF Applications with Intrinsic Delay and Stability as Design Tools, R. Chaujar, R. Kaur, M. Saxena, M. Gupta and R. S. Gupta, 2008 NSTI Nanotechnology Conference and Trade Show, June 1-5, 2008, Boston, Massachusetts, U.S.A. Nanotech 2008 Vol. 3, pp. 586-589

- 37. Compact Analytical Threshold Voltage Model for Nanoscale Multi-Layered-Gate Electrode Workfunction Engineered Recessed Channel, R. Chaujar, R. Kaur, M. Saxena, M. Gupta and R. S. Gupta, 2008 NSTI Nanotechnology Conference and Trade Show, June 1-5, 2008, Boston, Massachusetts, U.S.A. Nanotech 2008 Vol. 3, pp. 873-876

- 38. Nanoscale Analytical Modeling and TCAD Simulations of a Novel Gate Dielectric Stack SDPI MOSFET, Ravneet Kaur, Rishu Chaujar, **Manoj Saxena** and R.S. Gupta, **2<sup>nd</sup> IEEE International Nanoelectronics Conference** (INEC) Pudong, Shanghai in conjunction with the Shanghai Nanophotonics and Electronics Forum from 24-27 March 2008, pp 964-969

- 39. TCAD Investigation of Hot Carrier Reliability Issues Associated with GEWE-RC MOSFET, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, 2<sup>nd</sup> IEEE International Nanoelectronics Conference (INEC) Pudong, Shanghai in conjunction with the Shanghai Nanophotonics and Electronics Forum from 24-27 March 2008, pp. 1434-1437

- 40. Impact of Gate Stack Configuration onto the RF/analog Performance of ISE MOSFET., Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R. S. Gupta, International Conference of Recent Advances in Microwave Theory and Applications, Microwave-2008 conference, Nov. 21 24, 2008 at Jaipur, pp. 686-688.

- 41. GEWE-RC MOSFET: A solution to CMOS technology for RFIC design based on the concept of intercept point., Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, International Conference of Recent Advances in Microwave Theory and Applications, Microwave-2008 conference, Nov. 21 24, 2008 at Jaipur, pp. 661-663.

- 42. Impact of Multi-Layered Gate Design on Hot Carrier Reliability of Gate Electrode Workfunction Engineered Recessed Channel (GEWE-RC) MOSFET, R. Chaujar, R. Kaur, M. Saxena, M. Gupta and R. S. Gupta, XXIX General Assembly of the International Union of Radio Science (Union Radio Scientifique Internationale-URSI), Chicago, Illinois, USA on August 07-16, 2008.

- 43. GEWE-RC MOSFET: High Performance RF Solution to CMOS Technology, Rishu Chaujar, Ravneet Kaur, **Manoj Saxena**, Mridula Gupta and R.S. Gupta, **Asia Pacific Microwave Conference (APMC)-2008**, December 16-19, 2008 in Hong Kong Convention and Exhibition Center, Hong Kong, China, art. no. 4958185

- 44. TCAD Performance Investigation of a Novel MOSFET Architecture of Dual Material Gate Insulated Shallow Extension Silicon on Nothing MOSFET for the ULSI-Era, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R.S. Gupta, Asia Pacific Microwave Conference (APMC)-2008, December 16-19, 2008 in Hong Kong Convention and Exhibition Center, Hong Kong, China, art. no. 4958643

#### 2009

- 45. Analytical Drain Current Evaluation Technique for Various Non-Uniformly Doped MOS Device Architectures, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R.S. Gupta, International Symposium on Microwave and Optical Technology (ISMOT) 2009, December 16-19,2009 in Hotel Ashok, New Delhi, India

- 46. Evaluation of Multi-Layered Gate Design on GEWE-RC MOSFET for Wireless Applications in terms of Linearity-Distortion Issues, Rishu Chaujar, Manoj Saxena, Mridula Gupta and R.S. Gupta, International Symposium on Microwave and Optical Technology (ISMOT)-2009, December 16-19,2009 in Hotel Ashok, New Delhi, India

#### 2010

- 47. A Unified Two Dimensional Analytical Model of optically Controlled Silicon On Insulator MESFET (OPSOI) for advanced channel materials, Rajni Gautam, Manoj Saxena, R.S. Gupta and Mridula Gupta, The International Conference on Fiber Optics and Photonics PHOTONICS, December 11-15,2010, IIT Guwahati

- 48. A 2-D Subthreshold Analytical model for Short Channel Effects in Nanowire MOSFETs (Si, Ge), Gaurav Mahajan, Rakhi Narang, Manoj Saxena, V.K. Chaubey, Nirma University International Conference on Engineering (NUICONE) 2010, December 09-11, 2010, Nirma University, Ahmedabad

- **49.** Fabrication and Time degradation study of mercuric iodide (Red) single crystal X-Ray detector, Kulvinder Singh and **Manoj Saxena**, **International Symposium on Semiconductor Materials and Devices (ISSMD)**, M. S. University Vadodara, Gujarat, January 28-30, 2011

- 50. Nanoscale <u>Double Gate Silicon On Nothing</u> (DGSON) MOSFET: Promising Device Design for Wide Range of Operating Temperatures, Vandana Kumari, Manoj Saxena, Mridula Gupta and R. S. Gupta, International Conference on Latest Trends in Nanoscience and Nanotechnology (ICNSNT), 28<sup>th</sup> -29<sup>th</sup> March 2011, Karnataka, India

- 51. Impact of a low bandgap material on the Linearity of a DG-TFET: A Comparative Study, Rakhi Narang, Manoj Saxena, Mridula Gupta and R. S. Gupta, International Conference on Latest Trends in Nanoscience and Nanotechnology (ICNSNT), 28<sup>th</sup> -29<sup>th</sup> March 2011, Karnataka, India

- 52. Study of Performance Degradation of the Nanoscale Cylindrical Surrounding Gate MOSFET due to Hot Carrier Induced Localized Charges, Rajni Gautam, Manoj Saxena, Mridula Gupta and R. S. Gupta, International Conference on Latest Trends in Nanoscience and Nanotechnology (ICNSNT), 28<sup>th</sup> -29<sup>th</sup> March 2011, Karnataka, India

- 53. Immunity Against Temperature Variability and Bias Point Invariability in Double Gate Tunnel Field Effect Transistor, Rakhi Narang, Manoj Saxena, R. S. Gupta and Mridula Gupta, International Conference on Materials for Advance Technologies, (ICMAT 2011), June 26, 2011 July 01, 2011, Singapore

- 54. SiGe Metal Semiconductor Field Effect Transistor (MESFET) Photodectetor Having Tailorable Photoresponse Using Bandgap Engineering, Rajni Gautam, Manoj Saxena, R. S. Gupta and Mridula Gupta, International Conference on Materials for Advance Technologies, (ICMAT 2011), June 26, 2011 July 01, 2011, Singapore

- 55. Simulation Study of Insulated Shallow Extension Silicon On Nothing (ISESON) MOSFET for High Temperature Applications, Vandana Kumari, Manoj Saxena, R. S. Gupta and Mridula Gupta, International Conference on Materials for Advance Technologies, (ICMAT 2011), June 26, 2011 July 01, 2011, Singapore

- 56. High Sensitivity Photodetector Using Si/Ge/GaAs Metal Semiconductor Field Effect Transistor (MESFET), Rajni Gautam, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, **OPTICS 2011**, May 23-25, 2011, Calicut, Kerala, India

- 57. Impact of Localized Charges on RF and Microwave Performance of Nanoscale Cylindrical Surrounding Gate MOSFET, Rajni Gautam, Manoj Saxena, R. S. Gupta and Mridula Gupta, 13<sup>th</sup>International Symposium on Microwave and Optical Technology, ISMOT 2011, Prague, Czech Republic, EU, June 20-23, 2011

- 58. RF Performance Analysis of Double Gate Tunneling Field Effect Transistor (DG-TFET), Rakhi Narang, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, **13**<sup>th</sup> **International Symposium on Microwave and Optical Technology, ISMOT 2011**, Prague, Czech Republic, EU, June 20-23, 2011

- 59. Comparative Study of Dielectric Pocket (DP) MOSFET Incorporating Buried Oxide Layer (BOX) with DP MOSFET for RF Applications, Vandana Kumai, Manoj Saxena, R. S. Gupta and Mridula Gupta, 13<sup>th</sup> International Symposium on Microwave and Optical Technology, ISMOT 2011, Prague, Czech Republic, EU, June 20-23, 2011

- 60. Effect of Temperature and Gate Stack on the Linearity and Analog Performance of Double Gate Tunnel FET, Rakhi Narang, Manoj Saxena, R. S. Gupta and Mridula Gupta, The Second International Workshop on VLSI (VLSI 2011) in conjunction with (NECOM-2011), Venue: The Park Hotels, July 15 ~ 17, 2011, Chennai, India.

- 61. Channel Material Engineered Nanoscale Cylindrical Surrounding Gate MOSFET With Interface Fixed Charges, Rajni Gautam, Manoj Saxena, R. S. Gupta and Mridula Gupta, The Second International Workshop on VLSI (VLSI 2011) in conjunction with (NECOM-2011), Venue: The Park Hotels, July 15 ~ 17, 2011, Chennai, India.

- 62. An Analytical Modeling Approach for a Gate All Around (GAA) Tunnel Field Effect Transistor (TFET), Rakhi Narang, **Manoj**Saxena, R. S. Gupta and Mridula Gupta, *Accepted for Publication in XVI International Workshop on the Physics of Semiconductor Devices, IWPSD 2011, December 19-22, 2011, IIT Kanpur*

- 63. Digital Circuit Analysis of Insulated Shallow Extension Silicon On Void (ISESOV) FET for Low Voltage Applications, Vandana Kumai, Manoj Saxena, R. S. Gupta and Mridula Gupta, Accepted for Publication in XVI International Workshop on the Physics of Semiconductor Devices, IWPSD 2011, December 19-22, 2011, IIT Kanpur

- 64. Influence of Localised charges on the temperature sensitivity of Si nanowire MOSFET, Rajni Gautam, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, *Accepted for Publication in XVI International Workshop on the Physics of Semiconductor Devices, IWPSD 2011, December 19-22, 2011, IIT Kanpur*

- 65. Stability Study on Ceramic Mercuric Iodide (Red) X-Ray Sensor, Singh and **Manoj Saxena**, Accepted for Publication in XVI International Workshop on the Physics of Semiconductor Devices, IWPSD 2011, December 19-22, 2011, IIT Kanpur

- 66. Modeling and Simulation of Dielectric Pocket Double Gate (DP-DG) MOSFET for Low Voltage Low Power Analog Applications, Vandana Kumai, Manoj Saxena, R. S. Gupta and Mridula Gupta, Accepted for Publication in 2011 International Semiconductor Device Research Symposium, December 07-09, 2011, University of Maryland, USA

- 67. Analytical Model of a Tunnel FET Based Biosensor for Label Free Detection, Rakhi Narang, K V Sasidhar Reddy, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, *Accepted for Publication in 2011 International Semiconductor Device Research Symposium, December 07-09, 2011, University of Maryland, USA*

- 68. Investigation of RF/Microwave Performance Degradation for Cylindrical Nanowire MOSFET Due to Interface (Localised) Charges, Rajni Gautam, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, *Accepted for Publication in 2011 International Semiconductor Device Research Symposium*, *December 07-09*, 2011, University of Maryland, USA

- 69. Drain Current Model of Nanoscale Dual Material Gate (DMG) MOSFET including interfacial hot-carrier-induced degradation effect", Mini, Vandana Kumai, Manoj Saxena, R. S. Gupta and Mridula Gupta, Accepted for Publication in International Conference on Microwaves, Antenna, Propogation and Remote Sensiing, ICMARS-2011

# Paper Published in National conferences: -

#### 2004

1. Two-Dimensional Analytical Modeling and Simulation of DMG-EPI MOSFET, Kirti Goel, **Manoj Saxena**, Mridula Gupta and R. S. Gupta, **National conference on VLSI Design & Technology**, April 12-13, 2004, Bharati Vidyapeeth's College of Engineering, Paschim Vihar, New Delhi, India.

#### 2005

- Two-Dimensional Analytical Modeling and Simulation of a novel structure Triple-Material Gate Stack (TRIMGAS) MOSFET, R. S. Gupta, Kirti Goel, Manoj Saxena and Mridula Gupta, ELECTRO-2005, Emerging Trends in Electronics, BHU, Varanasi, February 3-5, p.134-137, 2005.

- Two-Dimensional Analytical Modeling and Simulation of Multiple Material Gate Oxide Stacked MOSFET, R. S. Gupta, Kirti Goel, Manoj Saxena and Mridula Gupta, National Conference on Integrated Broad Band Digital Systems and Networks, NIEC, Delhi, March 18-19, 2005

#### 2006

- 4. RF Performance Investigation of Gate Stacked Insulated Shallow Extension (ISE) MOSFET and Bulk: A Comparative Study, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R. S. Gupta, Proceeding of Mathematical Techniques Emerging Paradigm for Electronics and IT Industries (MATEIT 2006), pp 254-258

- 5. Design and FPGA realization of Direct Sequence-Spread Spectrum (DS-SS) BPSK Modulator using a Five Stage Gold Code Generator, Rishu Chaujar, Ravneet Kaur, Manoj Saxena and R. S. Gupta, Proceeding of Mathematical Techniques Emerging Paradigm for Electronics and IT Industries (MATEIT 2006), pp 213-216.

- 6. Scrambled Sequence FPGA based Direct Sequence Spread Spectrum BPSK Modulator: 10 Stage Analysis, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R. S. Gupta, National Conference on Recent Trends in Electronics and Information Technology, (RTEIT 2006), pp 334-337, 28-29 July 2006, Maharashtra, India.

- Exploring the Effect of Negative Junction Depth on Electrical Behaviour of Sub-50-Nanometer Concave DMG MOSFET: A

Simulation Study, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R. S. Gupta, National Conference on Recent

Advancement in Microwave Technique and Applications (Microwave-2006), pp. 123-125, 6-8 October 2006, Jaipur, India.

- 8. Lateral Channel Engineered Structure- Insulated Shallow Extension (ISE) MOSFET: DC and RF Performance Investigation, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R. S. Gupta, National Conference on Recent Advancement in Microwave Technique and Applications (Microwave-2006), pp. 119-122, 6-8 October 2006, Jaipur, India.

# 2007

- Effect of transport property on the performance of insulated shallow extension gate stack (ISEGaS) MOSFET, Ravneet Kaur, Rishu Chaujar, Manoj Saxena and R. S. Gupta, Indian microelectronics Society Conference 2007 Theme: Trends in VLSI and Embedded System, pp. 52-57, August 17-18, 2007, Punjab Engineering College, Chandigarh, India

- New Concave MOSFET with Transverse Dual Material Gate (T-DMG) in Sub-50nm Regime: A Simulation Study, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta and R. S. Gupta, Indian microelectronics Society Conference 2007 Theme: Trends in VLSI and Embedded System, pp. 33-37, August 17-18, 2007, Punjab Engineering College, Chandigarh, India (Best Student Paper Award)

- 11. A 2-D Analytical Model for Gate Misalignment Effects on Graded Channel DG FD SOI n-MOSFET, Rupendra Kumar Sharma, Manoj Saxena, Mridula Gupta and R. S. Gupta, Indian microelectronics Society Conference 2007 Theme: Trends in VLSI and Embedded System, August 17-18, 2007, Punjab Engineering College, Chandigarh, India

2008

- 12. Development Board-Level Experimentation and Simulation of FPGA based DEBPSK DSSS Modulator: Implementation of 10-Chip Gold Code Sequence Generator, Rishu Chaujar, Ravneet Kaur, Manoj Saxena and R. S. Gupta, Second National Conference on Mathematical Techniques Emerging Paradigm for Electronics and IT Industries (MATEIT 2008) September 26-28, 2008 in New Delhi, India, pp. 255-261.

- 13. Simulation of a Novel ISE MOSFET with Gate Stack Configuration, Ravneet Kaur, Rishu Chaujar, **Manoj Saxena** and R. S. Gupta, **Second National Conference on Mathematical Techniques Emerging Paradigm for Electronics and IT Industries (MATEIT 2008)** September 26-28, 2008 in New Delhi, India, pp. 291-296.

- 14. Solution to CMOS technology for high performance analog applications: GEWE-RC MOSFET, Rishu Chaujar, Ravneet Kaur, Manoj Saxena, Mridula Gupta, R. S. Gupta, 2<sup>nd</sup> National Workshop on Advanced Optoelectronic Materials and Devices, AOMD 2008, art. no. 5075707, pp. 201-205.

#### 2011

- Effect of temperature variation on various parameters in Insulated Shallow Extension Silicon On Nothing(ISE-SON)MOSFET:A simulation study, Vandana Kumari, Manoj Saxena, R. S. Gupta and Mridula Gupta, National Conference and Workshop on Recent Advances in Modern Communication Systems and Nanotechnology (NCMCN – 2011), January, 06-08, 2011

- Performance Comparison of Silicon and SiGe based Double Gate Tunneling Field Effect Transistor with gate stack architecture, Rakhi Narang, Manoj Saxena, R. S. Gupta and Mridula Gupta, National Conference and Workshop on Recent Advances in Modern Communication Systems and Nanotechnology (NCMCN – 2011), January, 06-08, 2011

- 17. Impact of Localised Charges on the performance of the Si Nanowire Surrounding Gate MOSFET, Rajni Gautam, Manoj Saxena, R. S. Gupta and Mridula Gupta, National Conference and Workshop on Recent Advances in Modern Communication Systems and Nanotechnology (NCMCN 2011), January, 06-08, 2011

- 18. Simulation Study of Stack Gate Insulated Shallow Extension Silicon On Nothing ISE-SON MOSFET for RFICs design, Vandana Kumari, **Manoj Saxena**, R. S. Gupta and Mridula Gupta, **2011 IEEE Students' Technology Symposium** at IIT Kharagpur during 14-16 January 2011, pp. 286-291.

- 19. Modeling and Simulation of multi layer gate dielectric Double Gate Tunnel Field-Effect Transistor (DG-TFET), Rakhi Narang, Manoj Saxena, R. S. Gupta and Mridula Gupta, 2011 IEEE Students' Technology Symposium at IIT Kharagpur during 14-16 January 2011.

- Analysis and Simulation of Si/GaAs/GaN MESFET to study the impact of Localised charges on device performance, Rajni Gautam, Manoj Saxena, R. S. Gupta and Mridula Gupta, 2011 IEEE Students' Technology Symposium at IIT Kharagpur during 14-16 January 2011, pp. 259-264

- 21. Mixedmode Circuit Simulation of Silicon and Germanium Nanowire MOSFETs A Comparative Study, Gaurav Mahahan, Rakhi Narang, **Manoj Saxena** and V. K. Chaubey, **2011 IEEE Students' Technology Symposium** at IIT Kharagpur during 14-16 January 2011, pp. 292-296.

- 22. Investigation of Linearity Performance of a Double Gate Band to Band Tunnel Field Effect Transistor, Rakhi Narang, **Manoj** Saxena, R. S. Gupta and Mridula Gupta, **15**<sup>th</sup> VLSI Design and Test Symposium, July 7-9, 2011, Wipro Technologies, Pune, India

- 23. Analog Performance of Insulated Shallow Extension Silicon On Nothing (ISE-SON) MOSFET: Simulation study, Vandana Kumari, Manoj Saxena, R. S. Gupta and Mridula Gupta, 15<sup>th</sup> VLSI Design and Test Symposium, July 7-9, 2011, Wipro Technologies, Pune, India

- 24. A Wide Temperature Range (50-500K) Analysis For Nanoscale Surrounding Cylindrical Gate MOSFET With Localised Charges, Rajni Gautam, Manoj Saxena, R. S. Gupta and Mridula Gupta, 15<sup>th</sup> VLSI Design and Test Symposium, July 7-9, 2011, Wipro Technologies, Pune, India

#### Other publications (Edited works, Book reviews, Festschrift volumes, etc.)

- **Member Editorial Board -** Proceedings of 16th Asia Pacific Microwave Conference 2004, Department of Electronic Science, University of Delhi, Allied Publishers Pvt. Ltd. 2004, ISBN 81-7764-722-9.

- Proceeding Editor National Conference on Mathematical Techniques: Emerging Paradigms for Electronics and IT Industries (MATEIT-2006) from 22<sup>nd</sup> March – 25<sup>th</sup> March 2006, Deen Dayal Upadhyaya College, University of Delhi, Shivaji Marg, New Delhi, India, ISBN: 81-8424-026-0

- **E-Proceeding Editor** National Conference on Mathematical Techniques: Emerging Paradigms for Electronics and IT Industries (MATEIT-2008) from 26<sup>th</sup> September 28<sup>th</sup> September 2008, Deen Dayal Upadhyaya College, University of Delhi, Shivaji Marg, New Delhi, India

- Editor Proceeding of the International Symposium on Microwave and Optical Technology (ISMOT)-2009, December 16-19,

Proceeding Editor - Third National Conference on Mathematical Techniques: Emerging Paradigms for Electronics and IT Industries (MATEIT-2010) held during January 30-31, 2010, Deen Dayal Upadhyaya College, University of Delhi, Shivaji Marg, New Delhi, India, sponsored By University Grants Commission (UGC), Govt. of India

#### Citation of My work: - (as on September 20, 2011)

H-Index - 6 (Author ID: 7102970979) http://www.scopus.com/scopus/home.url

• Sum of the Times Cited (after eliminating Self-citations): 125

My papers in the area of Electron Devices (published during the last 9 years) have received following citations till date (as indexed in the Google scholar, Thomson ISI, Science Citation Index and Scopus).

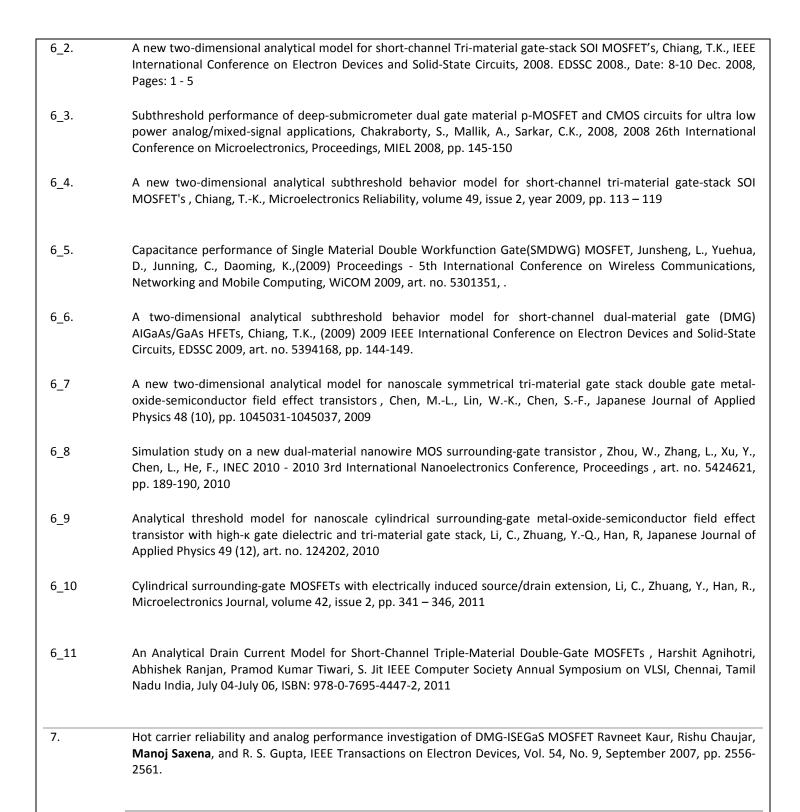

Physics Based Analytical Modeling of Potential and Electrical Field Distribution in Dual Material Gate (DMG)-MOSFET for Improved Hot Electron Effect and Carrier Transport Efficiency, Manoj Saxena, Subhasis Haldar, Mridula Gupta, and R. S. Gupta, IEEE Transaction on Electron Devices, Vol. 49, No. 11, pp. 1928-1938, November 2002

#### **Times Cited: 34**

- 1\_1. Ph. D Dissertation titled Hot-carrier reliability simulation in aggressively scaled MOS transistors, Manish P. Pagey, Faculty of the Graduate School of Vanderbilt University, 2003, Nashville, Tennessee

- 1\_2. Nanoscale device architecture to reduce leakage currents through quantum-mechanical simulation, A. A. P. Sarab and Deepanjan Datta, Sudeb Dasgupta, Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures, Vol. 24, No.3, pp. 1384-1397, May 2006

- 1\_3. Novel nanoscale device architecture to reduce leakage currents in logic circuits: a quantum-mechanical study, Deepanjan Datta, Samiran Ganguly, S Dasgupta and A Annada Prasad Sarab, Semiconductor Science Technology Vol.21, pp. 397-408, 2006.

- 1\_4. Analytical Modeling of Dual Material Gate SOI MOSFET with Asymmetric Halo, Li Zun-chao, Jiang Yao-lin, Zhang Li, Journal of China University of Mining & Technology (English Edition) Vol.16, No.3, pp. 308-311, 2006

- 1\_5. Silicon Complementary Metal–Oxide–Semiconductor Field-Effect Transistors with Dual Work Function Gate, Kee-Yeol Na and Yeong-Seuk Kim, Japanese Journal of Applied Physics, Vol. 45, No. 12, pp. 9033-9036, 2006

- 1\_6. Master Thesis titled, Analysis of DC and AC behavior of dual-material (DM) double-gate (DG) fully-depleted (FD) silicon on insulator (SOI) MOS device Rai-Min Huang, Graduate Institute of Electronic Engineering, Electronic Engineering Institute, Taiwan University, 2006

- 1\_7. Study of leakage current in novel nanoscale device architecture depending on doping profile, Datta, D., 2006, Journal of Computational and Theoretical Nanoscience, Vol. 3, No. 2, pp. 301-311

- 1\_8. A New Two-Dimensional Analytical Model for Short-Channel Symmetrical Dual-Material Double-Gate Metal-Oxide—Semiconductor Field Effect Transistors, Te-Kuang Chiang and Mei-Li Chen, Japanese Journal of Applied Physics, Vol. 46, No. 6A, pp. 3283-3290, 2007

| 1_9.  | Pearson-IV type doping distribution-based analytical modeling of dual-material double-gate fully-depleted silicon-on-insulator MOSFET, Alok Kushwaha, Manoj K Pandey, A. K Gupta, Microwave and Optical technology Letter, Vol. 49, No. 4, pp. 979-986, April 2007                          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1_10. | A Pseudo Two-Dimensional Subthreshold Surface Potential Model for Dual-Material Gate MOSFETs, S. Baishya, A. Mallik, C. K. Sarkar, IEEE transactions on Electron Devices Vol. 54 No.9, pp. 2520-2525, September 2007                                                                        |

| 1_11. | Two-dimensional model of fully depleted dual-material-gate single-halo SOI MOSFET, Li, ZC., Jiang, YL., Wu, JM. 2007 Tien Tzu Hsueh Pao/Acta Electronica Sinica 35 (2), pp. 212-215                                                                                                         |

| 1_12. | Subthreshold current model of fully depleted dual material gate SOI MOSFET, Su, J., Li, Z., Zhang, L. 2007 Academic Journal of Xi'an Jiaotong University 19 (2), pp. 135-137                                                                                                                |

| 1_13. | Design considerations of Sub-100nm Dual Material Gate Fully Depleted Silicon On Insulator (DMG-FD-SOI), Jafar, Norsyahida; Soin, Norhayati, IEEE International Conference on Semiconductor Electronics, 2008. ICSE 2008, Date: 25-27 Nov. 2008, Pages: 69 - 75                              |

| 1_14. | Two dimensional analytical modeling of multi-layered dielectric G 4 MOSFET-A novel design, Gupta, R.S., Sharma, N., Bansal, J., Chaujar, R., Gupta, M., 2008 International Conference of Recent Advances in Microwave Theory and Applications, MICROWAVE 2008, pp. 47-49                    |

| 1_15  | A new analytical subthreshold behavior model for single-halo, dual-material gate silicon-on-insulator metal oxide semiconductor field effect transistor, Chiang, TK., Japanese Journal of Applied Physics, Vol. 47, No.11, pp. 8297-8304, 2008                                              |

| 1_16  | New analytical model for short-channel fully depleted dual-material gate silicon-on-insulator metal semiconductor field-effect transistor, Chiang, TK., Japanese Journal of Applied Physics, Vol. 47, No.12, pp. 8743-8748, 2008                                                            |

| 1_17  | The new analytical subthreshold behavior model for dual material gate (DMG) SOI MESFET, Chiang, TK., International Conference on Solid-State and Integrated Circuits Technology Proceedings, ICSICT, pp. 288-292, 2008                                                                      |

| 1_18  | A new two-dimensional analytical model for short-channel Tri-material gate-stack SOI MOSFET's, Chiang, T.K., IEEE International Conference on Electron Devices and Solid-State Circuits, 2008. EDSSC 2008., Date: 8-10 Dec. 2008, Pages: 1 - 5                                              |

| 1_19  | Subthreshold Performance of Dual-Material Gate CMOS Devices and Circuits for Ultralow Power Analog/Mixed-Signal Applications, Saurav Chakraborty, Abhijit Mallik, and Chandan Kumar Sarkar, IEEE Transaction on Electron Devices, Vol. 55, No. 3, pp. 827-832, March 2008                   |

| 1_20  | Subthreshold performance of deep-submicrometer dual gate material p-MOSFET and CMOS circuits for ultra low power analog/mixed-signal applications, Chakraborty, S., Mallik, A., Sarkar, C.K., 2008, 2008 26th International Conference on Microelectronics, Proceedings, MIEL 2008, pp. 145 |

| 1_21  | A new two-dimensional analytical subthreshold behavior model for short-channel tri-material gate-stack SOI MOSFET's, Te-Kuang Chiang, Microelectronics Reliability, Volume 49, Issue 2, Feb 2009, Pages 113-119                                                                             |

| 1_22 | Performance and optimisation of dual material gate short channel BULK MOSFETs for analogue/mixed signal applications, N. Mohankumar; Binit Syamal; C. K. Sarkar, International Journal of Electronics, Volume 96, Issue 6, Pages 603 – 611, 2009                                      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1_23 | A new compact subthreshold behavior model for dual-material surrounding gate (DMSG) MOSFETs, Te-Kuang Chiang, Volume 53, Issue 5, pp. 490-496, Solid State Electronics, 2009.                                                                                                         |

| 1_24 | A new two-dimensional subthreshold behavior model for the short-channel asymmetrical dual-material double-gate (ADMDG) MOSFET's, Chiang, TK., (2009) Microelectronics Reliability, 49 (7), pp. 693-698.                                                                               |

| 1_25 | Dual Material Gate Silicon on Insulator (DMGSOI) - Design impact on linearity, Jafar, N., Soin, N., (2009) Proceedings of 2009 5th International Colloquium on Signal Processing and Its Applications, CSPA 2009, art. no. 5069207, pp. 156-159.                                      |

| 1_26 | The microwave noise behaviour of Dual Material Gate silicon on insulator, Jafar, N., Soin, N., (2009) AIP Conference Proceedings, 1136, pp. 820-824.                                                                                                                                  |

| 1_27 | Investigation of novel attributes of single halo dual-material double gate MOSFETs for analog/RF applications, Mohankumar, N., Syamal, B., Sarkar, C.K., (2009) Microelectronics Reliability, 49 (12), pp. 1491-1497.                                                                 |

| 1_28 | A two-dimensional analytical subthreshold behavior model for short-channel dual-material gate (DMG) AlGaAs/GaAs HFETs, Chiang, T.K, (2009) 2009 IEEE International Conference on Electron Devices and Solid-State Circuits, EDSSC 2009, art. no. 5394168, pp. 144-149.                |

| 1_29 | Capacitance performance of Single Material Double Workfunction Gate(SMDWG) MOSFET, Junsheng, L., Yuehua, D., Junning, C., Daoming, K., (2009) Proceedings - 5th International Conference on Wireless Communications, Networking and Mobile Computing, WiCOM 2009, art. no. 5301351, . |

| 1_30 | Analog and short channel effects performance of sub-100 nm graded channel fully depleted silicon on insulator (SOI), Norsyahida Jafar and Norhayati Soin, Proceedings of the 8th WSEAS international conference on Microelectronics, nanoelectronics, optoelectronic (MINO'09)        |

| 1_31 | A New Two-Dimensional Analytical Model for Nanoscale Symmetrical Tri-Material Gate Stack Double Gate Metal—Oxide—Semiconductor Field Effect Transistors, Mei-Li Chen, Wen-Kai Lin, and Shih-Fang Chen, Japanese Journal of Applied Physics, 48 (2009) 104503 (7 pages)                |